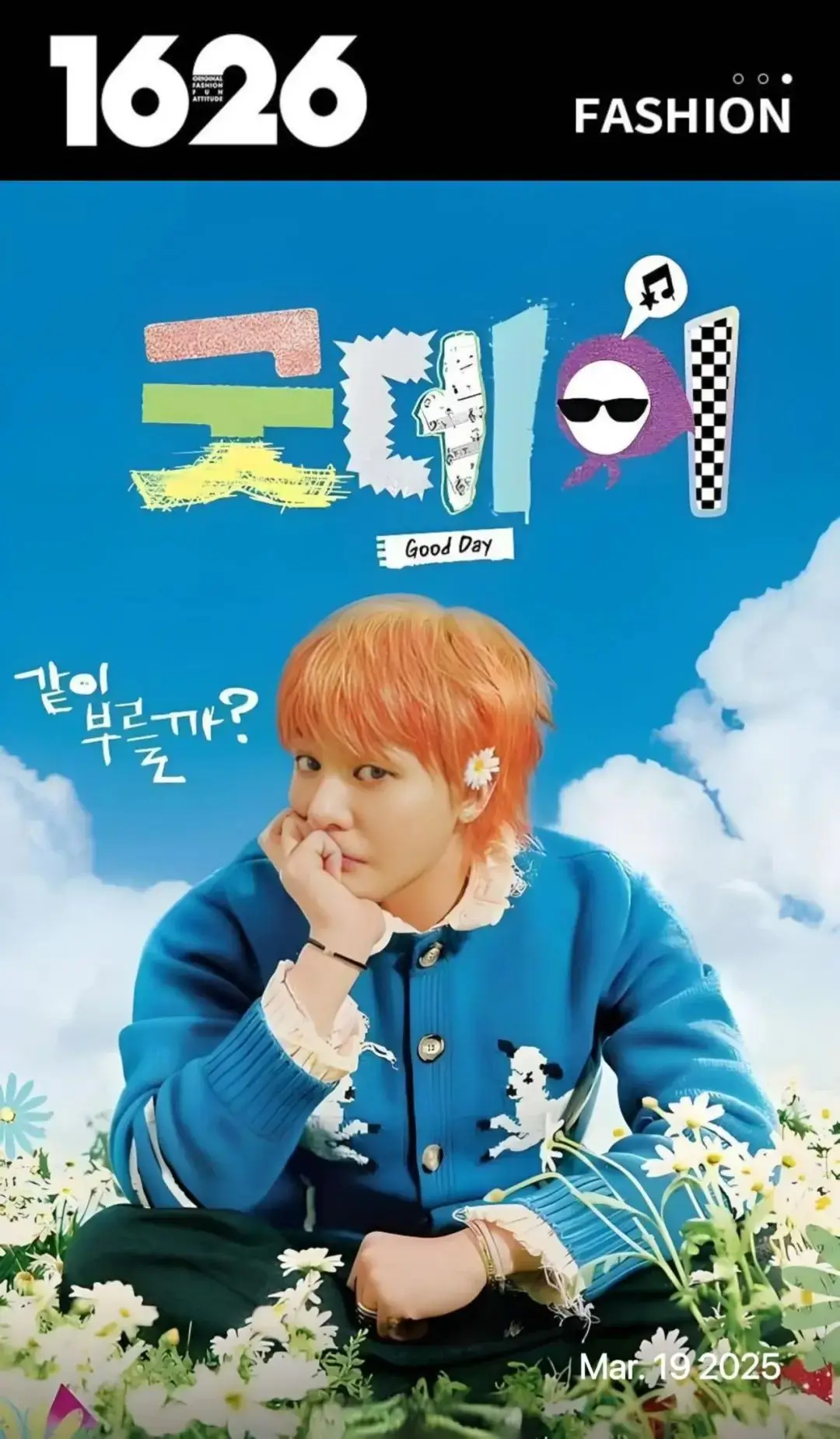

2024年堪稱權志龍粉絲的狂歡年。自去年底正式回歸以來,這位亞洲潮流教父接連帶來重磅驚喜:2月推出個人綜藝《Good Day》、發布暌違七年的概念專輯《Übermensch》,更宣布全球巡演計劃重啓。這位現象級藝人的多維回歸矩陣,持續點燃着粉絲的狂熱激情。

想必大家已經看過 GD 新專輯《Übermensch》中《POWER》和《TOO BAD》的MV,GD在其中的造型堪稱奢華。僅造型就有數十個,服飾花費高達數億韓元,更不用說珠寶、腕表等配飾的費用了。

展開全文

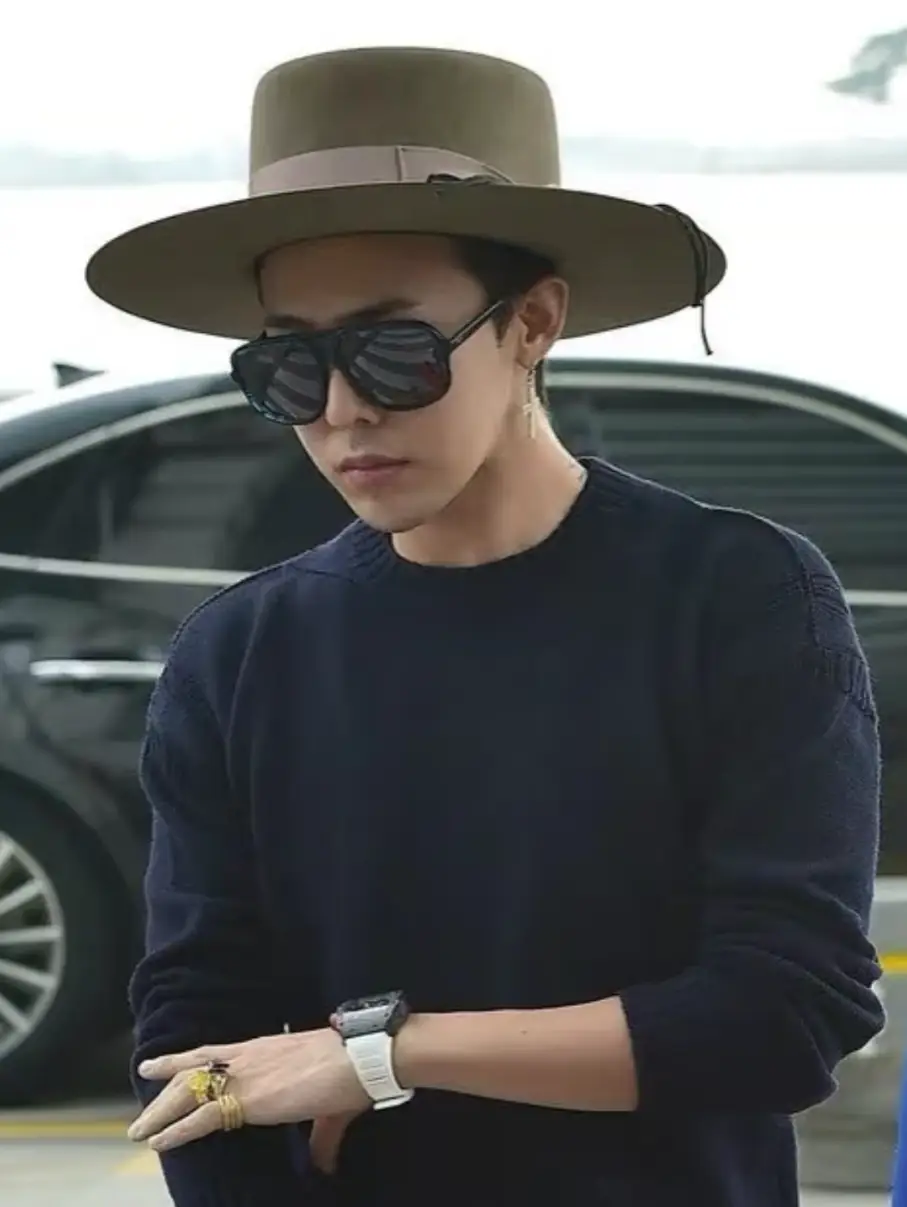

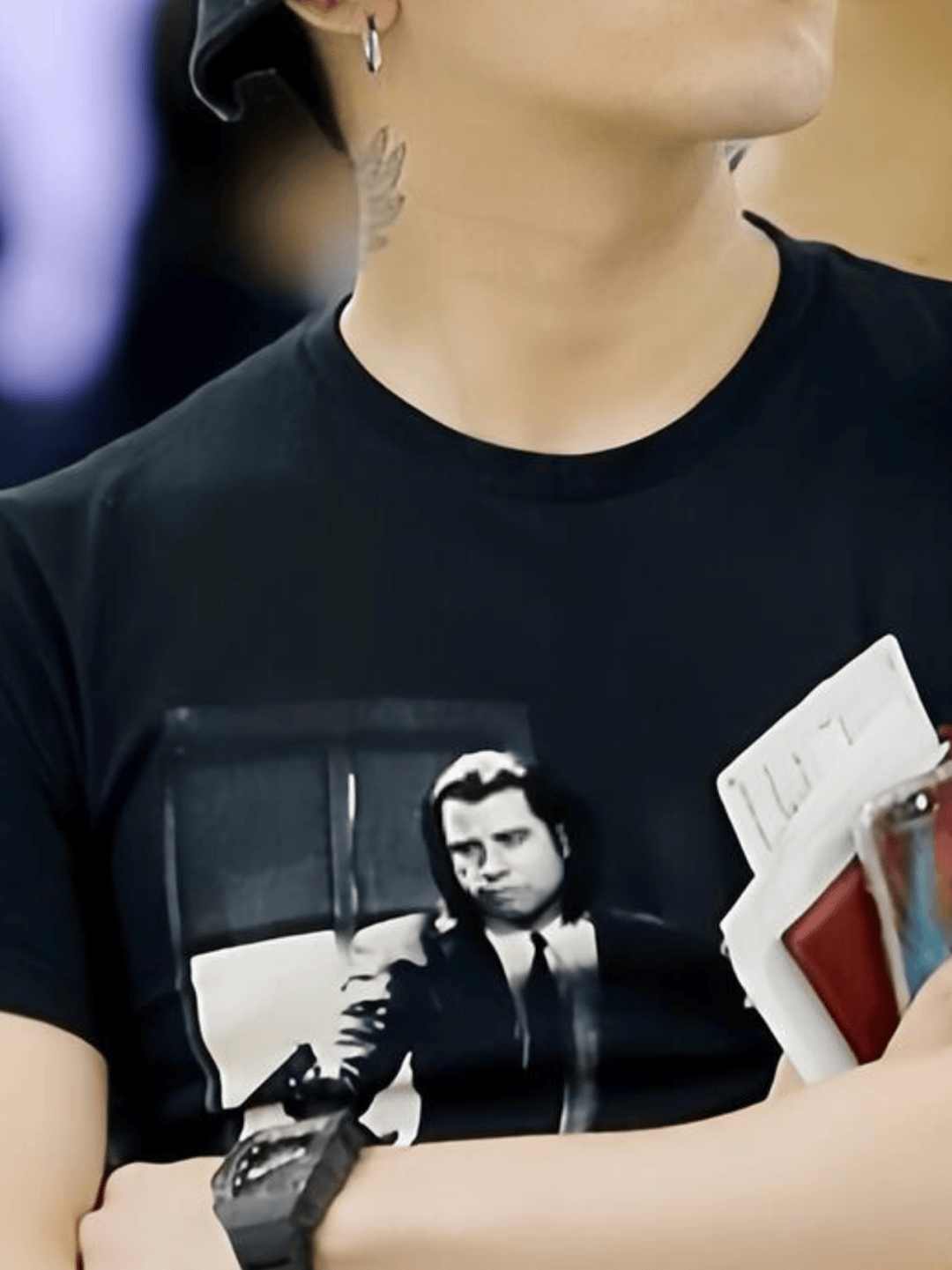

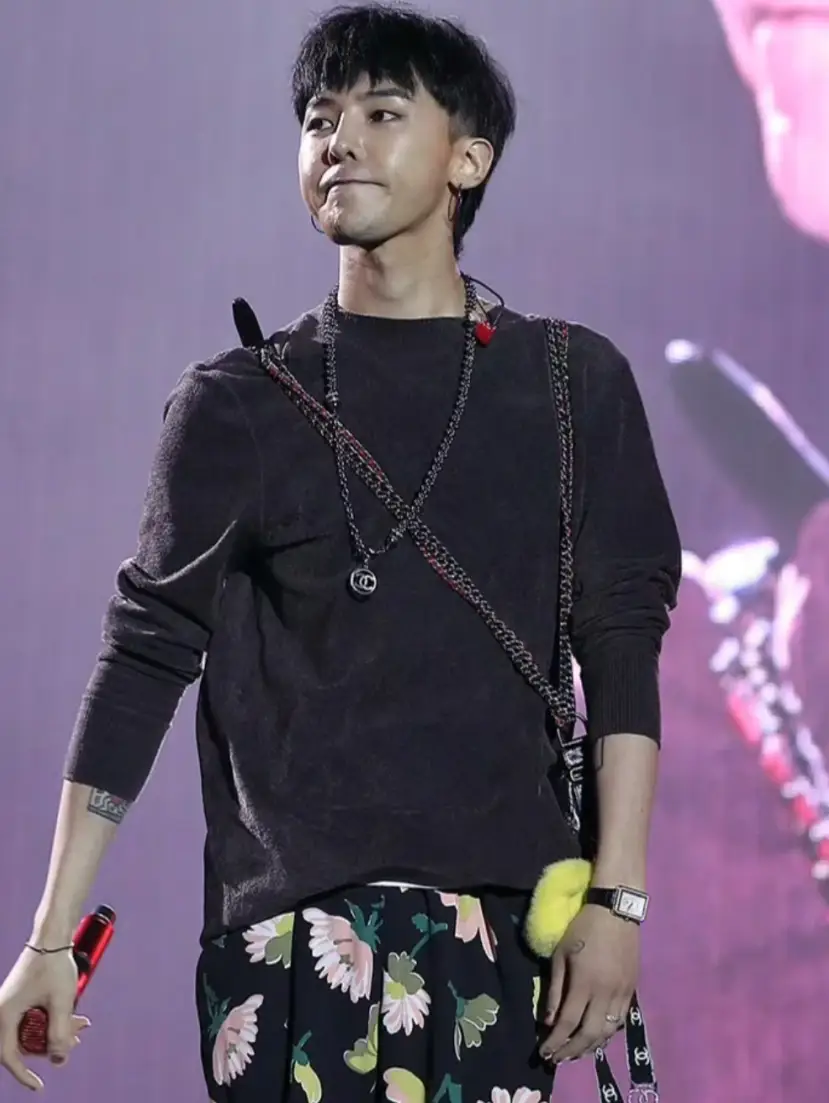

或許不是每個人都會喜歡 GD 的風格,但不可否認的是,他的每一次出現都會引發新的潮流話題。衆所周知,GD 的穿搭風格偏向極繁主義,他喜歡用各種色彩的珠寶和腕表來點綴整體造型。GD 的珠寶造型太過耀眼,常常成爲討論焦點,但很多人可能不知道,他其實是一位腕表狂熱愛好者。

奢華藝術

Jacob & Co.聯名傑作

在近期首爾舉行的 Jacob & Co. 旗艦店揭幕儀式上,品牌方邀請了衆多韓國明星,品牌摯友權志龍壓軸亮相,共同揭曉 Astronomia Solar Baguette 聯名腕表。

無論是在他的日常生活分享、MV 還是舞台上,他的珠寶飾品很大一部分都是來自 Jacob & Co. 。

這次活動雖然是品牌新店开業,但全場的焦點和亮點卻並非新店本身,而是 Jacob & Co. 公布的與權志龍的全新合作——雙方推出的定制腕表。

這款定制腕表的原型是 Jacob & Co. 的 Astronomia Solar Baguette,設計靈感源自宇宙行星,其普通款的定價就高達 78 萬美元,屬於超高端腕表。

Astronomia Solar Baguette 腕表的設計特點在於將表盤中央的刻度和太陽系行星以 Jacob-cut 各類奢華寶石球體呈現。

和權志龍的聯名款特別版在保留標志性寶石星軌設計基礎上,創新融入權志龍個人美學符號,除了加入他個人的標志性元素——小雛菊之外,原本的藍色地球也被改成了綠松石設計,並有玫瑰金的龍形立體環繞在外。玫瑰金色的表盤背面刻有權志龍新專輯《Übermensch》的字樣,表圈上還印有他的個人標語 “The world is mine”。

如此奢華的用料和設計,稱這塊腕表爲傳世藝術品也毫不誇張,其定價自然也是高得驚人——官方售價爲 14 億 300 萬韓元(約合 700 萬人民幣)。

不過,“好消息”是這款 GD x Jacob & Co.的 Astronomia Solar Baguette 對粉絲相當“友好”,全球限量 9 枚,其中韓國地區配貨3枚。相信有鈔能力的粉絲一定會爭相搶購。

機械美學

Richard Mille藏家圖鑑

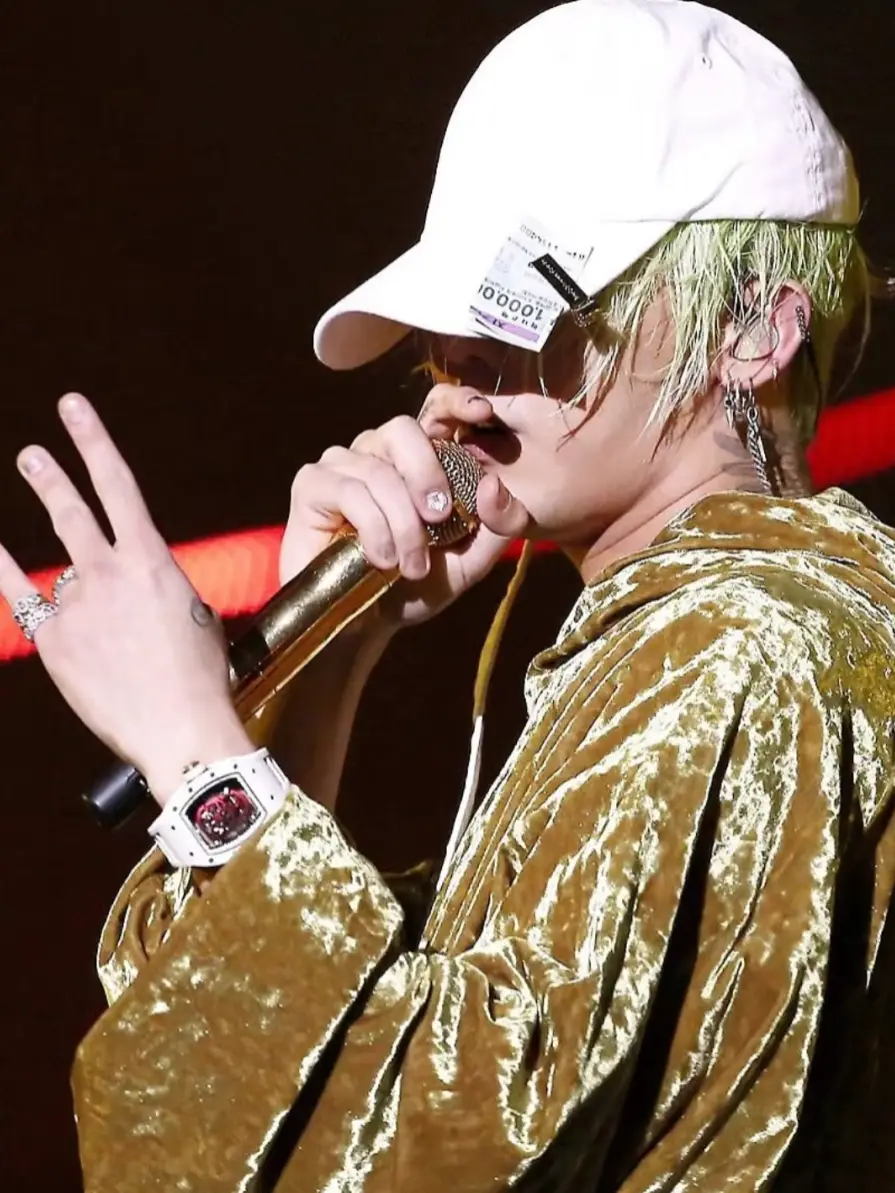

除了 Jacob & Co.,權志龍也是理查德米勒(Richard Mille)的忠實粉絲。他很早就开始佩戴該品牌的限量款腕表,並在公开場合至少展示過8款不同的理查德米勒腕表。

理查德米勒的魅力在於,它將機械表玩出了新花樣,每塊表都擁有讓人一眼就被徵服的精密機械結構,極具辨識度。而且,該品牌的腕表上市數量極少,有錢也未必能买到。因此,對於明星藝人來說,其吸引力不言而喻。

理查德米勒的熱門表型 RM52-01、RM35-01、RM011、RM11-03 等,權志龍幾乎都收入囊中。品牌方甚至爲他定制了獨一無二的專屬腕表,這也就不難理解他爲何會對理查德米勒如此情有獨鐘。

早在 2014 年,他在參加綜藝節目時就曾佩戴過亞洲限量五枚的 RM051-01 Tiger Dragon,這只腕表目前市價是 2 千萬,這無疑真的就是“有錢也买不到”的系列。

經典重構

Rolex的顛覆演繹

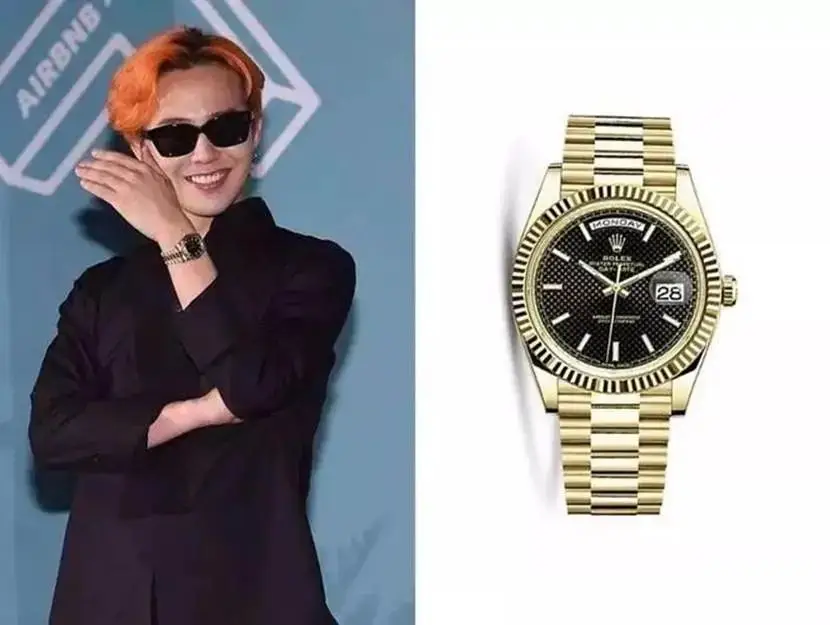

除了理查德米勒,權志龍也曾對勞力士(Rolex)情有獨鐘,其出鏡頻率相當高。此前,他在曬出 Chanel 新季飾品時,手上佩戴的 18K 金 Datejust 勞力士腕表就吸引了衆多關注。

GD還擁有一塊勞力士 Day Date 40 黃金牙圈黑面男表,其三角紋表圈相當經典,目前價值約 35 萬元人民幣。

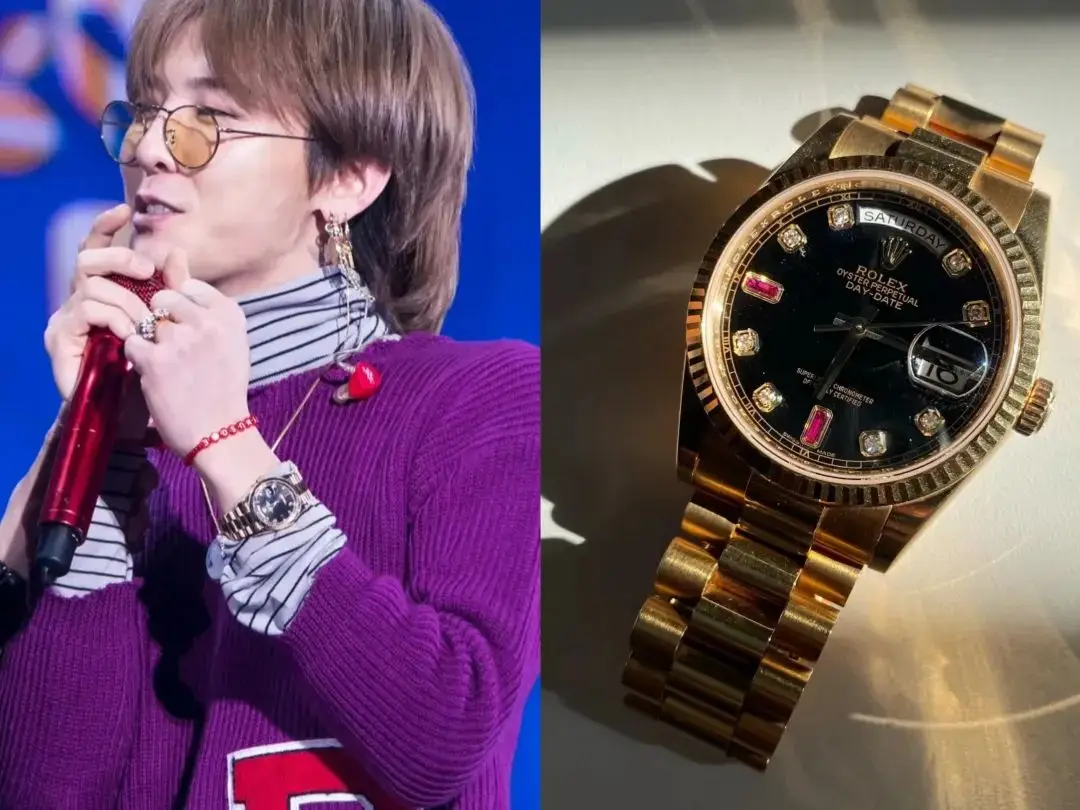

在表演中,GD曾經佩戴過一塊勞力士黑盤 Day Date 女表,69 數字位置鑲嵌紅寶石,顏值極高,難怪直到現在市面上一直有人求同款。

此外,他還被曝光過佩戴藤原浩的 fragment design x Rolex 閃電聯名款、紅盤蠔式恆動以及金盤等勞力士腕表。這些勞力士腕表已經成爲了他日常穿搭的普通單品。

作爲亞洲潮流圈的鼻祖級人物,權志龍早在十年前就定制了克羅心(Chrome Hearts)與勞力士合作的 Air King 改版腕表,並至少爆改了三只。

演繹華麗

顛覆CHANEL的性別界限

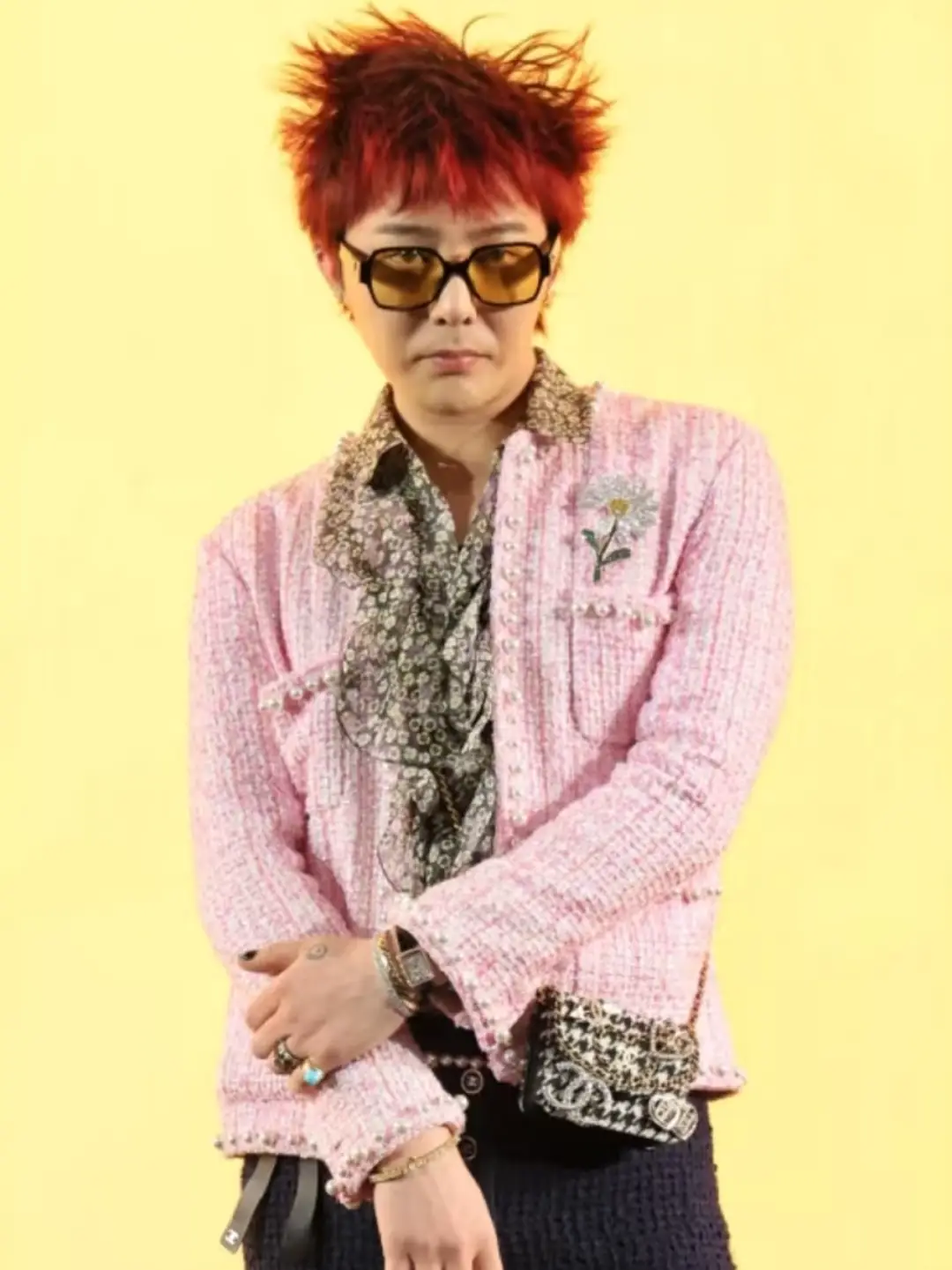

作爲 CHANEL 的全球代言人,CHANEL的各種高定、女裝服飾都被 GD 演繹成模糊了性別界限的中性美學風格,包括女款的腕表也是他經常選擇佩戴的產品。他所佩戴的表款都不是普通款式,被曝光的全都是鑲鑽款,相當豪氣。

他曾曬出過一款滿鑽 Chanel BoyFriend 腕表,鑲嵌了 501 顆鑽石,共 2.49 克拉,搭配鱷魚皮紋小牛皮表帶,官方價格高達 40 萬元人民幣。

懷舊中古

CARTIER的復古格調

不過,權志龍並非每天都會佩戴昂貴浮誇的名貴手表。就像是簡約造型的小方塊表也是他日常疊戴的凹造型單品之一。與他那些動輒幾十萬、上百萬的名表相比,他手上的 80 年代的中古款卡地亞 Tank 在他的駕馭下,也種草了一大批粉絲。而且,這些表款價格相對親民,萬元左右即可入手,性價比相當高。

日常實用

Casio&Apple Watch

除了理查德米勒、勞力士等頂級腕表品牌,權志龍也曾佩戴過一些實用型手表。比如,他在退伍時刻佩戴的 G-shock GA-110-1A ,當年一度被粉絲搶到全網斷貨。如今在二級市場,這款表僅需幾百元即可入手。

此外,智能手表 Apple Watch 一經發布,權志龍也第一時間展示了一番。作爲黑卡持有者的他,該省則省,該花則花,風格相當隨性。

標題:窮玩車富玩表,權志龍到底有多少頂級收藏

聲明: 本文版權屬原作者。轉載內容僅供資訊傳遞,不涉及任何投資建議。如有侵權,請立即告知,我們將儘速處理。感謝您的理解。